Key Features

Overview

Advanced Multi-Channel Logic Analysis for Professional Engineers

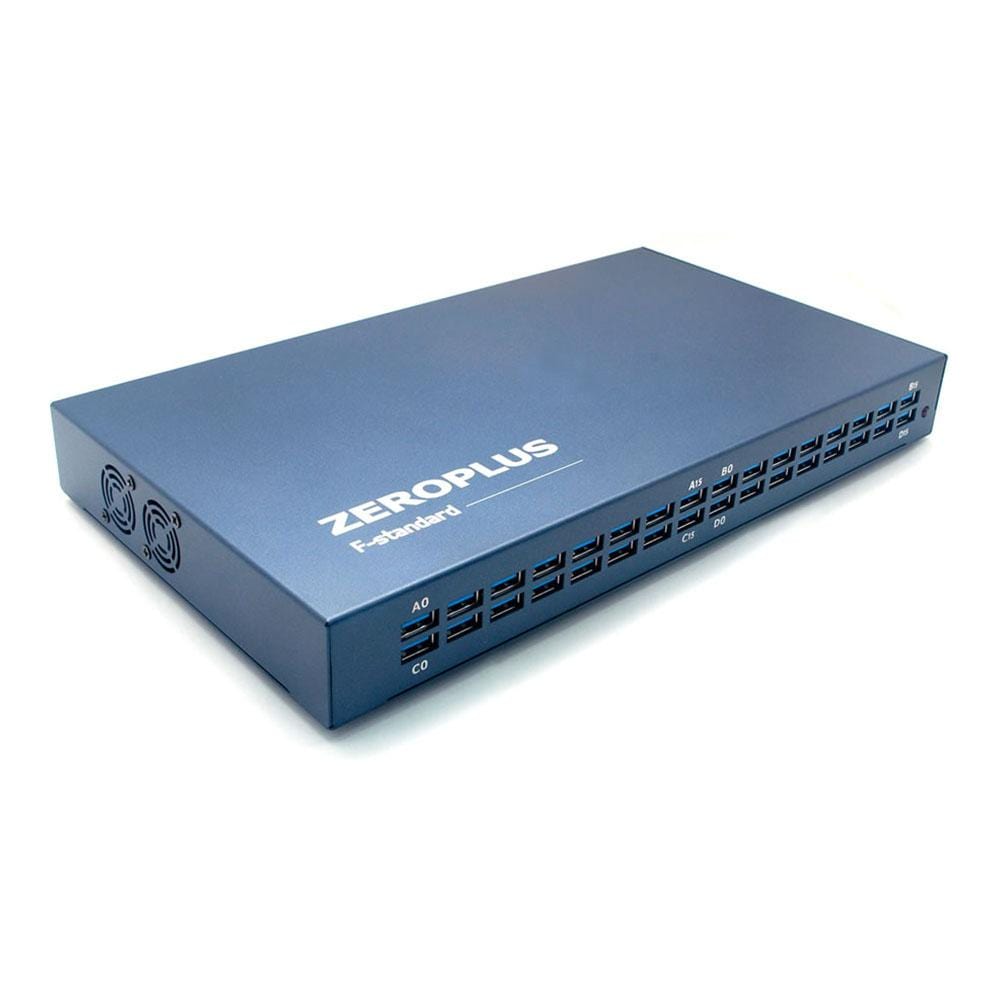

The ZeroPlus LAP-F Logic Analyser represents the pinnacle of PC-based logic analysis technology, delivering uncompromising performance for professional embedded system development. This sophisticated instrument combines high-speed 1GHz sampling rates with exceptional memory depth up to 64Mb per channel, making it ideal for debugging complex digital systems and validating high-speed protocols.

Professional-Grade Features

Available in 40-channel and 64-channel configurations, the LAP-F series offers flexible memory options from 4Mb to 64Mb per channel. The analyser excels at capturing long data sequences whilst maintaining precise timing resolution, essential for identifying intermittent faults and timing violations in modern digital designs.

The instrument includes over 110 built-in protocol decoders as standard, covering everything from I2C and SPI to advanced automotive protocols like CAN and LIN. The innovative Long-Time Record function enables continuous streaming directly to your computer's storage, allowing acquisition periods extending from hours to days - perfect for capturing elusive intermittent issues.

With its robust aluminium construction, comprehensive probe selection including specialised eMMC probes, and professional software suite, the LAP-F delivers the reliability and functionality demanded by serious electronics engineers developing next-generation embedded systems.

Downloads

Why Engineers Choose The ZeroPlus LAP-F High-Performance PC-Based Logic Analyser 40/64 Channel

Unmatched Signal Capture Depth

Professional Protocol Analysis

Long-Term Reliability Testing

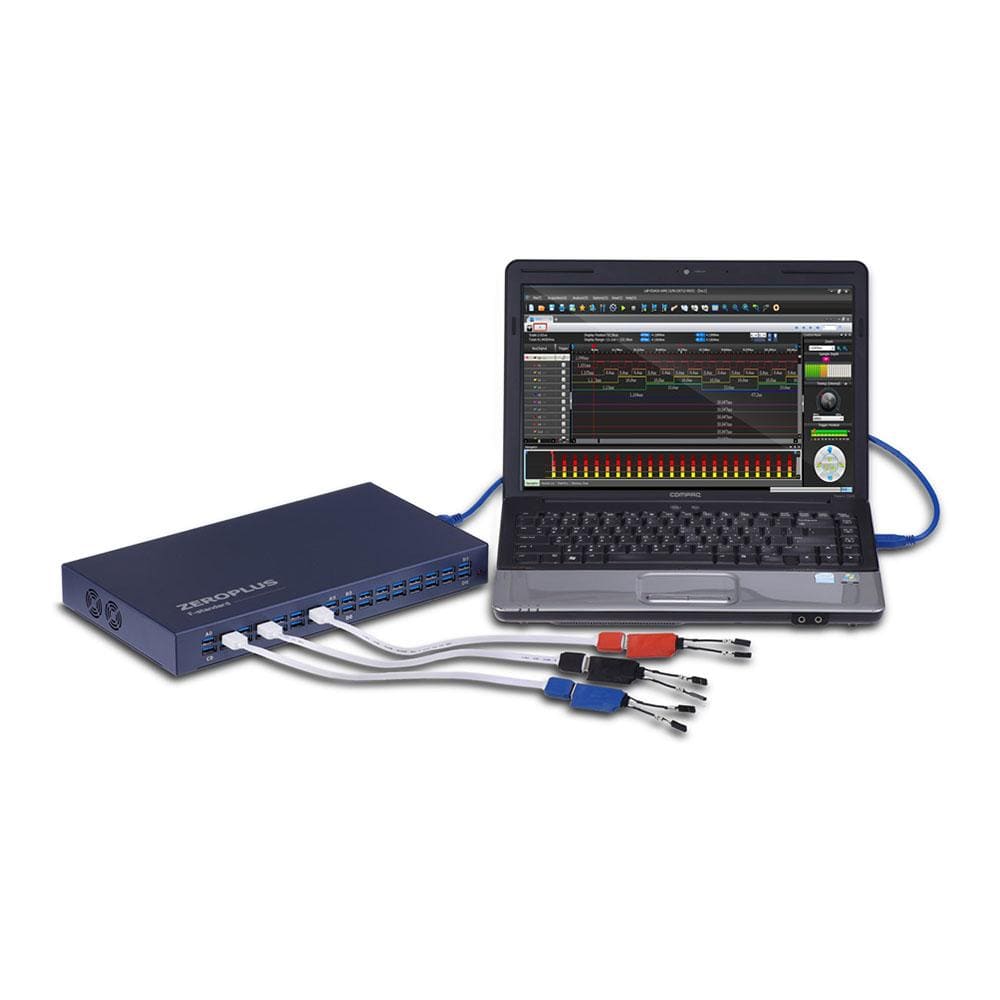

Extremely compact and lightweight, the ZeroPlus ZeroPlus-LAP-F logic analyser connects to and is powered by the USB port of any desktop or ZeroPlus-Laptop PC making it very portable and ideal for use in the field.

The ZeroPlus-LAP-F) provides internal sampling rates up to 1GHz and up to 512M samples memory depth per channel.

Trigger

- 6 protocol triggers (hardware)(serial): I2C, I2S, SPI, SVID, UART(RS-232C/422/485), CAN 2.0B

- Trigger types: Pattern / Edge / Pulse-Width / Interval

- Trigger channels: 40

- Trigger delay: Yes

- Trigger levels: 256

- Trigger pass: 1-65535

Special Software Features

- Zooming and panning

- Waveform and UI Customization

- State list and Waveform view

- Packet list

- Waveform Navigator

- Memory view

- Statistic

- File Comparison

Certifications

- FCC / CE

Active Probes/Signals

P120LV

P200EM (4 ch + 1 ch (CLK))

|

Protocol Analysis Feature

Over 130 different protocols can be analysed by the LAP-C logic analyser: .

- 1-Wire (Adv) Interface

- 1-Wire Interface

- 3-Wire Interface

- 7-segment LED Interface

- AC97 Interface

- AES/EBU Interface

- AMD SVI2 Interface

- Arithmetic Logic

- BDM Interface

- BMS Interface

- CAN 2.0B Bus

- CCIR656 Interface

- CMOS Image Sensor Interface

- Compact Flash 4.1 Interface

- DALI Interface

- Differential Manchester Interface

- Digital Logic

- DigRF Interface

- DMX512 Interface

- DP Aux Channel 1.1 Interface

- DSA Interface

- DSI Bus

- FlexRay 2.1A Bus

- FWH Interface

- GPIB/IEEE488 Interface

- HART Interface

- HD Audio Interface

- HDMI CEC Interface

- HDQ Interface

- HPI Interface

- I2C EEPROM 24L Memory Interface

- I2C EEPROM 24LCS Memory Interface

- I2C Interface

- I2S Interface

- ISO7816 UART Interface

- J-K Flip-flop

- JTAG 2.0 Interface

- KeeLoq Code Hopping Interface

- KNX Interface

- LCD12864 Display Interface

- LCD1602 Display Interface

- LED Pitch Array Interface

- LG4572 Interface

- LIN Bus 2.1

- Line Code

- LPC Bus

- LPC-SERIRQ Interface

- LPT Interface

- Manchester Encoding

- Maxim DS1302 Interface

- Maxim DS18B20 Interface

- MCU-51 Disassembly

- MDDI Interface

- MHL-CBus

- Microwire Bus

- Microwire EEPROM 93C

- MIDI Interface

- MII Interface

- Miller Interface

- MIPI CSI-2 Interface

- MIPI DSI Interface

- ModBus

- Modified Miller Interface

- Modified SPI Interface

- MVB

- NEC PD6122 Interface

- Opentherm 2.2 Interface

- PCI Bus

- PCM Interface

- PECI Interface

- Philips RC5 Interface

- Philips RC6 Interface

- ProfiBus

- PS/2 Interface

- PSB Interface

- PT2262/PT2272 Interface

- Quad SPI Interface

- RGB Interface

- S/PDIF Interface

- S2Cwire/AS2Cwire Interface

- Samsung K9 NAND Flash Interface

- SCCB Interface

- SD2.0/SDIO Interface

- SDQ Interface

- Serial GPIO IBPI Interface

- SHT11 Interface

- Signia 6210 Interface

- Single Wire Debug (SWD) Interface

- SITI DM114/DM115 Interface

- SLE4442 Interface

- SMBus 2.0

- SPI (Atmel 25F EEPROM)

- SPI Interface

- SPI Plus Interface

- SSI Interface

- ST7669 Interface

- STBus

- SVID Interface

- UART (RS-232C/RS-422/RS-485) Interface

- UNI/O Interface

- Up/Down Counter

- USB v1.1 Interface

- USB v2.0 Interface

- WIEGAND Interface

- WTB Bus

- WWV-WWVH-WWVB Interface

- YK-5 Interface

Test Probes

Ninety two Test probes are included with the basic analyser. Additional hooks are available as spares when needed.

| General Information | |

|---|---|

Part Number (SKU) |

LAP-F(14064M)

|

Manufacturer |

|

| Physical and Mechanical | |

Weight |

2.0 kg

|

| Other | |

Warranty |

|

HS Code Customs Tariff code

|

|

EAN |

5055383686735

|

Frequently Asked Questions

Have a Question?

-

How does the LAP-F compare to Keysight and Tektronix logic analysers?

The LAP-F provides comparable channel count and sampling rates to premium solutions but at significantly lower cost, includes more built-in protocol decoders, and offers superior memory depth per channel for extended captures.

-

What is the trigger capability of the LAP-F?

The LAP-F features a 256-level trigger sequence engine supporting pattern, edge, pulse-width, interval, and protocol-based triggering with hardware trigger support for I2C, SPI, UART, CAN, and other protocols.

-

Can the LAP-F analyse eMMC and SD card interfaces?

Yes, with optional eMMC 5.1/SD 3.0 capability, the LAP-F provides 32 channels at 2GHz sampling specifically for eMMC/SD analysis, including specialised triggering and decoding functions.

-

What makes the LAP-F superior to entry-level USB logic analysers?

Unlike streaming USB analysers, the LAP-F's buffered architecture eliminates USB bandwidth limitations, provides deeper memory, offers professional triggering capabilities, and includes comprehensive protocol analysis software.

-

Does the LAP-F support Windows 10?

Yes, the LAP-F supports Windows 7, 8.1, and 10. Windows 10 compatibility is fully supported with the latest software versions from ZeroPlus.

-

What probe types are included with the LAP-F?

The LAP-F includes low-voltage probes (P120LV) for each channel plus 4 eMMC probes. Optional TTL, negative logic, and high-speed eMMC/SD probes are available separately for specialised applications.

-

How does the Long-Time Record function work?

Long-Time Record streams captured data directly to your computer's hard drive at up to 300MB/s via USB 3.0, enabling continuous acquisition from 7 hours to 35 days depending on sampling configuration.

-

What memory depths are available for the LAP-F series?

The LAP-F offers flexible memory configurations from 4Mb to 64Mb per channel. Channel folding technology allows concentrating total memory across fewer channels for even deeper per-channel memory.

-

How many protocol decoders are included with the LAP-F?

The LAP-F includes over 110 built-in protocol decoders covering automotive (CAN, LIN), embedded (I2C, SPI, UART), and advanced protocols (eMMC, USB) with no additional licensing required.

-

What is the maximum sampling rate of the LAP-F Logic Analyser?

The ZeroPlus LAP-F offers 1GHz internal sampling rate for timing analysis and 200MHz for external state analysis, providing industry-leading capture capabilities for high-speed digital systems.